EtherCAT for PMCtendo DD5 and PMCprotego D

Servo amplifiers

This document is the original document.

All rights to this documentation are reserved by Pilz GmbH & Co. KG. Copies may be made for the user's internal purposes. Suggestions and comments for improving this documentation will be gratefully received.

Source code from third-party manufacturers or open source software has been used for some components. The relevant licence information is available on the Internet on the Pilz homepage.

Pilz®, PIT®, PMI®, PNOZ®, Primo®, PSEN®, PSS®, PVIS®, SafetyBUS p®, SafetyEYE®, SafetyNET p®, the spirit of safety® are registered and protected trademarks of Pilz GmbH & Co. KG in some countries.

| Section 1 | Genera                    | linformation                                        | 4  |  |  |  |  |

|-----------|---------------------------|-----------------------------------------------------|----|--|--|--|--|

|           | 1.1                       | About this manual                                   | 4  |  |  |  |  |

|           | 1.2                       | Target group                                        | 4  |  |  |  |  |

|           | 1.3 Definition of symbols |                                                     |    |  |  |  |  |

|           | 1.4                       | Abbreviations used                                  | 6  |  |  |  |  |

|           |                           |                                                     |    |  |  |  |  |

| Section 2 | Safety                    |                                                     | 8  |  |  |  |  |

|           | 2.1                       | Intended use                                        | 8  |  |  |  |  |

|           | 2.2                       | Notes on the online edition (PDF format)            | 9  |  |  |  |  |

| Section 3 | Inetalla                  | tion/commissioning                                  | 10 |  |  |  |  |

|           | 3.1                       | Assembly/installation                               | 10 |  |  |  |  |

|           | 3.1.1                     | Connection technology                               | 10 |  |  |  |  |

|           | 3.1.2                     | Commissioning                                       | 11 |  |  |  |  |

|           | 3.1.2.1                   | Guide to commissioning                              | 11 |  |  |  |  |

|           | 3.1.2.2                   | EtherCAT commissioning                              | 12 |  |  |  |  |

|           |                           |                                                     |    |  |  |  |  |

| Section 4 | EtherCA                   | AT                                                  | 13 |  |  |  |  |

|           | 4.1                       | Slave Register                                      | 13 |  |  |  |  |

|           | 4.2                       | AL event (interrupt event) and interrupt enable     | 14 |  |  |  |  |

|           | 4.2.1                     | Interrupt enable register (address 0x0204:0205)     | 14 |  |  |  |  |

|           | 4.2.2                     | AL Event (address 0x220:0221)                       | 14 |  |  |  |  |

|           | 4.3                       | Phase runup                                         | 15 |  |  |  |  |

|           | 4.3.1                     | AL Control (address 0x0120:0x0121)                  | 15 |  |  |  |  |

|           | 4.3.2                     | AL Status (address 0x0130:0x0131)                   | 16 |  |  |  |  |

|           | 4.3.3                     | AL Status Code (address 0x0134:0x0135)              | 16 |  |  |  |  |

|           | 4.3.4                     | EtherCAT communication phases                       | 17 |  |  |  |  |

|           | 4.4                       | CANopen over EtherCAT (CoE) state machine           | 18 |  |  |  |  |

|           | 4.4.1                     | Description of states                               | 19 |  |  |  |  |

|           | 4.4.2                     | Commands in the control word                        | 20 |  |  |  |  |

|           | 4.4.3                     | Bits of the status machine (status word)            | 21 |  |  |  |  |

|           | 4.5                       | Implemented operating modes                         | 22 |  |  |  |  |

|           | 4.6                       | Setting the EtherCAT cycle time                     | 22 |  |  |  |  |

|           | 4.7                       | Recommended cycle time based on the operating modes | 23 |  |  |  |  |

|           | 4.8                       | Synchronisation based on the cycle time             | 23 |  |  |  |  |

|           | 4.9                       | Latch- control word and latch status word           | 24 |  |  |  |  |

|           | 4.10                      | Mailbox Handling                                    | 25 |  |  |  |  |

|           | 4.10.1                    | Mailbox Output                                      | 26 |  |  |  |  |

|           | 4.10.2                    | Mail Input                                          | 27 |  |  |  |  |

|           | 4.10.3                    | Example of a mailbox access                         | 28 |  |  |  |  |

## 1 General information

## 1.1 About this manual

This manual describes the assembly, installation and commissioning of the "Expansion card EtherCAT" for servo amplifiers of the PMCprotego D series and a reference of the commands that are supported by these servo amplifiers.

The "Expansion card EtherCAT" provides an EtherCAT interface to this servo amplifier. The operating manual describes the card and its installation at a later stage.

In PMCprotego D the EtherCAT functionality is already integrated. The servo amplifier has an onboard Ethernet- interface that has been configured in the standard version for the EtherCAT protocols. This manual is a component of the overall documentation of the digital servo amplifiers. Installation and commissioning of the servo amplifiers and all the standard functions are described in the relevant operating manual.

## 1.2 Target group

This manual is aimed at qualified personnel with the following requirements:

| Transport     | Only by personnel with knowledge of managing electrostatically sensitive assemblies              |

|---------------|--------------------------------------------------------------------------------------------------|

| Unpacking     | Only by specialists with electrotechnical qualification                                          |

| Installation  | Only by specialists with electrotechnical qualification                                          |

| Commissioning | Only by specialists with extensive knowledge of electrical engineer-<br>ing and drive technology |

| Programming   | Software developer, EtherCAT design engineers                                                    |

The qualified staff must know and observe the following standards:

- IEC 60364 and IEC 60664

- National accident prevention regulations

## 1.3 Definition of symbols

Information that is particularly important is identified as follows:

### DANGER!

This warning must be heeded! It warns of a hazardous situation that poses an immediate threat of serious injury and death and indicates preventive measures that can be taken.

### WARNING!

This warning must be heeded! It warns of a hazardous situation that could lead to serious injury and death and indicates preventive measures that can be taken.

### CAUTION!

This refers to a hazard that can lead to a less serious or minor injury plus material damage, and also provides information on preventive measures that can be taken.

### NOTICE

This describes a situation in which the product or devices could be damaged and also provides information on preventive measures that can be taken. It also highlights areas within the text that are of particular importance.

### INFORMATION

This gives advice on applications and provides information on special features.

## 1.4 Abbreviations used

| Abbreviation    | Meaning                                                                                                                                                                                                  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AL              | Application Layer: The protocol used dir-<br>ectly by the process instances.                                                                                                                             |

| Cat             | Category - Classification also for the cables<br>used for Ethernet communication. EtherCAT<br>cables must be classified at least in cat-<br>egory 5.                                                     |

| DC              | Distributed Clocks Mechanism (Distributed Clock procedure) to sychronise EtherCAT-Slaves and Masters.                                                                                                    |

| DL              | Data Link, also Layer 2. EtherCAT used in accordance with IEEE 802.3 standardised Ethernet communication.                                                                                                |

| EtherCAT (ECAT) | RT standard for industrial Ethernet Control Automation Technology                                                                                                                                        |

| FPGA            | Field Programmable Gate Array (logic block that can be modified on-site)                                                                                                                                 |

| FTP             | File Transfer Protocol                                                                                                                                                                                   |

| HW              | Hardware                                                                                                                                                                                                 |

| ICMP            | Internet Control Message Protocol: Protocol to display IP errors.                                                                                                                                        |

| IEC             | International Electrotechnical Commission:<br>International standardisation committee                                                                                                                    |

| IEEE            | Institute of Electrical and Electronics Engin-<br>eers, Inc.                                                                                                                                             |

| IOS/OSI Model   | ISO Open Systems Interconnection Basic<br>Reference Model (ISO 7498) (ISO-OSI layer<br>model): Describes the dividing of the com-<br>munication in seven layers.                                         |

| LLDP            | Lower Layer Discovery Protocol                                                                                                                                                                           |

| MAC             | Media Access Control                                                                                                                                                                                     |

| MII             | Media Independent Interface: Standard in-<br>terface between Ethernet Controller and the<br>routers.                                                                                                     |

| MDI             | Media-independent interface:<br>Signal transmission using pins.                                                                                                                                          |

| MDI-X           | Media-dependent interface (crossover):<br>Crossed wiring                                                                                                                                                 |

| OSI             | Open System Interconnect                                                                                                                                                                                 |

| OUI             | Organizationally Unique Identifier - the first<br>3 Bits of an Ethernet address. They are as-<br>signed to companies or organisation and<br>the can also be used for Protocol Identifiers<br>(e.g.LLDP). |

| Abbreviation | Meaning                                                                                                                           |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|

| PDI          | Physical Device Interface: A set of physical elements that enable access from the process side.                                   |

| PDO          | Process Data Object                                                                                                               |

| PDU          | Protocol Data Unit: Includes protocol inform-<br>ation from a protocol instance via transpar-<br>ent data to a subordinate layer. |

| Ping         | Program for checking the accessibility of the partner device.                                                                     |

| РНҮ          | Physical interface, data conversion in elec-<br>trical or optical signals.                                                        |

| PLL          | Phase Locked Loop                                                                                                                 |

| РТР          | Precision Time Protocol in accordance with IEEE 1588                                                                              |

| RSTP         | Rapid Spanning Tree Protocol                                                                                                      |

| RT           | Real-time, possible in Ethernet Controller without additional support.                                                            |

| RT Frames    | EtherCAT transmission with EtherType 0x88A4.                                                                                      |

| RX           | Receive                                                                                                                           |

| RXPDO        | Receive PDO                                                                                                                       |

| SNMP         | Simple Network Management Protocol                                                                                                |

| SPI          | Serial Peripheral Interface                                                                                                       |

| Src Addr.    | Source Address: Source address of a trans-<br>mission.                                                                            |

| STP          | Shielded Twisted Pair                                                                                                             |

| ТСР          | Transmission Control Protocol                                                                                                     |

| ТХ           | Transmit                                                                                                                          |

| TXPDO        | Transmit PDO                                                                                                                      |

| UDP          | User Datagram Protocol: Unsafe Multicast-<br>Broadcast protocol                                                                   |

| UTP          | Unshielded Twisted Pair                                                                                                           |

| XML          | Extensible Markup Language                                                                                                        |

| XML Parser   | Program for checking XML structures                                                                                               |

| ZA ECAT      | Access type EtherCAT                                                                                                              |

| ZA Drive     | Access type amplifier                                                                                                             |

#### 2 Safety

### WARNING!

Risk of death or serious injury and material damage during operation

The operator must ensure that the safety guidelines in this manual are taken into account. The operator must ensure that every person entrusted with work at the servo amplifier have read and understood this operating manual.

We offer training and induction courses on request.

#### 2.1 Intended use

Please note the chapters "Intended use" and "Improper use" in the operating manual of the servo amplifier.

The sole purpose of the EtherCAT interface is to connect the servo amplifier to a Master with EtherCAT connection.

The servo amplifiers are installed as components in electrical apparatus or machinery and can only be commissioned as integrated plant components.

#### INFORMATION

We guarantee compliance of the servo amplifier with the following standards in the industrial sector only when using the components named by us and when complying with the installation manual: EU EMC Directive 2004/42/EG

EU Low Voltage Directive 2006/95/EG

## 2.2 Notes on the online edition (PDF format)

Bookmarks:

Table of contents and index are active bookmarks.

Table of contents and index in the text:

The lines are active cross-references. Click the required line to display the corresponding page.

Page number in the text:

Page numbers/chapter numbers with cross references are active. Click on the page number/chapter number to go to the specified target. 3 Installation/commissioning

## 3.1 Assembly/installation

### WARNING!

### **Risk of electrocution!**

Install and wire the devices always in a voltage-free state. Ensure that there is a safe enabling of the control cabinet (lock, warning signs etc.). The individual voltages are switched on only when commissioning. Residual charges in the capacitors may still show hazardous values several minutes after the mains voltage is switched off. Measure the voltage in the intermediate circuit and wait until the voltage has dropped below 40 VDC. Control and power connections may still carry voltage, even when the motor is not rotating.

### WARNING!

### Possible loss of the safety

Electronic devices are not fail-safe as a matter of principle. The user is responsible that the drive is led to a safe condition for machinery or personnel when the servo amplifier fails, e.g. by using a mechanical brake. Drives with servo amplifiers in EtherCAT networks are remotely operated machines. They can set in motion at any time without prior notice. Warn the operator and maintenance personnel by corresponding instructions. Use a relevant protective measure to ensure that an unintended startup of the machine does not lead to a hazardous situation for man and machine. Software end switches do not replace the hardware end switches of the machine.

#### NOTICE

Wire the servo amplifier as described in the operating manual. The wiring of the analogue set value input and the position interface after the connection image of the operating manual may be omitted.

### INFORMATION

Due to the internal representation of the position control parameters, the position controller can only be operated if the final speed of the drive does not exceed the following values:

rotary:

Sinusoidal<sup>2</sup>-shaped acceleration: max. 7500 U/min

Trapezoidal acceleration: max. 12000 U/min

linear:

Sinusoidal<sup>2</sup>-shaped acceleration: max. 4 m/s

Trapezoidal acceleration: max. 6.25 m/s

### INFORMATION

All the data regarding resolution, incremental value, positioning accuracy etc. refers to the arithmetic values. Non-linearities in the mechanics (back-lash, elasticity etc.) are not considered.

If the motor's end speed needs to be changed, all the position control and motion block parameters that were entered previously will need to be adapted.

## 3.1.1 Connection technology

Connection to the EtherCAT network via RJ45 connector (IN and OUT interfaces).

## 3.1.2 Commissioning

### 3.1.2.1 Guide to commissioning

### INFORMATION

The servo amplifier may only be commissioned by qualified personnel with sound knowledge of control and drive technology.

## CAUTION!

### Possible loss of the safety

Ensure that no hazard can result for personnel or machinery, even if the drive should move unintentionally.

#### Procedure:

| Step                                     | Description                                                                                                                                                                                                                                       |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Check assembly/installation              | Check that all the safety guidelines in this<br>manual and in the operating manual for the<br>servo amplifier are respected and imple-<br>mented.                                                                                                 |

| Connect PC, start commissioning software | Use the commissioning software to set the parameters for the servo amplifier.                                                                                                                                                                     |

| Commissioning the basic functions        | Commission the basic functions of the servo<br>amplifier and optimise the current, speed<br>and position controller. This part of the com-<br>missioning process is described in more de-<br>tail in the commissioning software's online<br>help. |

| Save parameters                          | Once the parameters have been optimised they should be saved in the servo amplifier.                                                                                                                                                              |

### 3.1.2.2 EtherCAT commissioning

To commission with the TwinCAT tool please use the documents in the download area of the Pilz homepage.

To commission with the motion controller PMCprimo please use the documents in the download area of the Pilz homepage.

# 4 EtherCAT

## 4.1 Slave Register

The following table displays the addresses of individual registers in the FPGA memory. The data exist in little endian format, the "least significant byte" is on the lower address. A de-tailed description of all registers and FPGA locations can be seen from the "EtherCAT Slave Controller" description of the EtherCAT user organisation (www.ethercat.org).

| Address    | Lengt<br>h<br>(Byte) | Description                                               | ZA<br>ECAT | ZA<br>Drive |

|------------|----------------------|-----------------------------------------------------------|------------|-------------|

| 0x0120     | 2                    | AL Control                                                | r/w        | r/-         |

| 0x0130     | 2                    | AL Status                                                 | r/-        | r/w         |

| 0x0134     | 2                    | AL Status Code                                            | r/-        | r/w         |

| 0x0204     | 2                    | Interrupt enable register                                 | r/-        | r/w         |

| 0x0220     | 2                    | AL Event (IRQ Event)                                      | r/w        | r/-         |

| 0x0800     | 8                    | AL Manager 0 (Mail Out control register)                  | r/w        | r/-         |

| 0x0808     | 8                    | AL Manager 1 (Mail Out control register)                  | r/w        | r/-         |

| 0x0810     | 8                    | AL Manager 2 (Process data Output Control Register)       | r/w        | r/-         |

| 0x0818     | 8                    | AL Manager 3 (Process data Input Control Re-<br>gister)   | r/w        | r/-         |

| 0x0820     | 8                    | AL Manager 4                                              | r/w        | r/-         |

| 0x0828     | 8                    | AL Manager 5                                              | r/w        | r/-         |

| 0x0830     | 8                    | AL Manager 6                                              | r/w        | r/-         |

| 0x0838     | 8                    | AL Manager 7                                              | r/w        | r/-         |

| 0x0840     | 8                    | AL Manager 8                                              | r/w        | r/-         |

| 0x1100     | 64                   | ProOut Buffer (process data output, set values ECAT)      | r/w        | r/-         |

| 0x1140     | 72                   | ProIn (process data input, actual values of ECAT)         | r/-        | r/w         |

| 0x1800     | 512                  | Mail Out Buffer (Object channel buffer of ECAT)           | r/w        | r/-         |

| 0x1C00     | 512                  | Mail In Buffer (Object channel buffer of serve amplifier) | r/-        | r/w         |

|            |                      |                                                           |            |             |

| *:ZA ECA   | r = Acces            | ss type EtherCAT                                          |            |             |

| ZA Drive = | Access               | type amplifier                                            |            |             |

## 4.2 AL event (interrupt event) and interrupt enable

The communication between the drive and EtherCAT FPGA is completely interrupt-controlled. The Interrupt enable register and the AI event register are responsible for the interrupt functionality of the EtherCAT interface. With a 1 in the corresponding Bit of the Interrupt enable register the servo amplifier activates the individual events of the EtherCAT interface, with a 0 the events are deactivated.

| Parameter               | Address | Bit | ZA<br>Drive | ZA<br>ECAT | Description                                                                                          |

|-------------------------|---------|-----|-------------|------------|------------------------------------------------------------------------------------------------------|

| AL Control<br>Event     | 0x204   | 0   | r/w         | r          | Activating the AL Control Events for phase runup                                                     |

|                         | 0x204   | 1   | r/w         | r          | Reserved                                                                                             |

| DC Distributed<br>Clock | 0x204   | 2   | r/w         | r          | Activating the Distributed Clock<br>(DC) Interrupts for the complete<br>communication                |

|                         | 0x204   | 3 7 | r/w         | r          | Reserved                                                                                             |

| Mail Out Event          | 0x205   | 0   | r/w         | r          | Activating the Mailbox Output<br>Event (SDO, Sync Manager 0)<br>for the object channel               |

| Mail In Event           | 0x205   | 1   | r/w         | r          | Activating the Mailbox Input<br>Event (SDO, Sync Manager 1)<br>for the object channel                |

| Pro Out Event           | 0x205   | 2   | r/w         | r          | Activating the process data<br>Output Event (PDO, cyclical set<br>values of the card)                |

| Pro In Event            | 0x205   | 3   | r/w         | r          | Activating the process data In-<br>put Event (PDO, cyclical actual<br>values of the servo amplifier) |

|                         | 0x205   | 4 7 | r/w         | r          | Reserved                                                                                             |

### 4.2.1 Interrupt enable register (address 0x0204:0205)

With a 1 in the relevant Bit of the AL Event register the EtherCAT interfaces signals to the servo amplifier in the Interrupt routine which event is to be processes by the servo amplifier.

## 4.2.2 AL Event (address 0x220:0221)

| Parameter                       | Address | Bit | ZA<br>Drive | ZA<br>ECAT | Description                                   |

|---------------------------------|---------|-----|-------------|------------|-----------------------------------------------|

| AL Control Event                | 0x220   | 0   | r           | r/w        | Editing the AL Control Events for phase runup |

| Sync Manager<br>Watchdog Event  | 0x220   | 1   | r           | r/w        | Editing a Sync Manager Watch-<br>dog Event    |

| Distributed Clock<br>(DC) Event | 0x220   | 2   | r           | r/w        | Editing a Distributed Clock (DC)<br>Event     |

|                                 | 0x220   | 3 7 | r           | r/w        | Reserved                                      |

|                                              |         |     | ZA          | ZA   |                                                                                                      |

|----------------------------------------------|---------|-----|-------------|------|------------------------------------------------------------------------------------------------------|

| Parameter                                    | Address | Bit | ZA<br>Drive | ECAT | Description                                                                                          |

| Sync Manager 0<br>Event                      | 0x221   | 0   | r           | r/w  | Activating the Mailbox Output<br>Event (SDO, Sync Manager 0)<br>for the object channel               |

| Sync Manager 1<br>Event                      | 0x221   | 1   | r           | r/w  | Activating the Mailbox Input<br>Event (SDO, Sync Manager 1)<br>for the object channel                |

| Sync Manager 2<br>Event                      | 0x201   | 2   | r           | r/w  | Activating the process data Out-<br>put Event (PDO, cyclical set val-<br>ues of the card)            |

| Sync Manager 3                               | 0x201   | 3   | r           | r/w  | Activating the process data Input<br>Event (PDO, cyclical actual val-<br>ues of the servo amplifier) |

| Sync Manager 4<br>– Sync Manager<br>7 Event  | 0x221   | 4 7 | r           | r/w  | Reserved                                                                                             |

| Sync Manager 8<br>– Sync Manager<br>15 Event | 0x222   | 0 7 | r           | r/w  | Reserved                                                                                             |

## 4.3 Phase runup

The registers AL Control, AL Status and AL Status Code are responsible for the communication phase runup (also called EtherCAT change of state) and the display of the current status and any error messages are the registers AL Control, AL Status und AL Status Code. Each Transition request of the EtherCAT interface by the AL Control Register and each AL Control Event (Interrupt) is followed by the servo amplifier with the AL Status Register. Any error messages are displayed in the AL Status Code Register.

### 4.3.1 AL Control (address 0x0120:0x0121)

| Parameter            | Address | Bit  | ZA<br>Drive | ZA<br>ECAT | Description                                                                                                                                       |

|----------------------|---------|------|-------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Status               | 0x120   | 3 0  | R           | w          | 0x01: Init Request<br>0x02: PreOperational Request<br>0x03: Bootstrap Mode Request<br>0x04: Safe Operational Request<br>0x08: Operational Request |

| Acknow-<br>ledgement | 0x120   | 4    | R           | w          | 0x00: No error reset<br>0x01: Error reset with positive<br>pulse edge                                                                             |

| Reserved             | 0x120   | 7 5  | R           | w          |                                                                                                                                                   |

| Appl. specific       | 0x120   | 15 8 | R           | w          |                                                                                                                                                   |

## 4.3.2 AL Status (address 0x0130:0x0131)

| Parameter       | Address | Bit  | ZA<br>Drive | ZA<br>ECAT | Description                                                                                                               |

|-----------------|---------|------|-------------|------------|---------------------------------------------------------------------------------------------------------------------------|

| Status          | 0x130   | 3 0  | w           | r          | 0x01: Init<br>0x02: PreOperational<br>0x03: Bootstrap Mode<br>0x04: Safe Operational<br>0x08: Operational                 |

| Change of state | 0x130   | 4    | W           | r          | 0x00: Confirmation during change of<br>state<br>0x01: Error during change of state,<br>e.g. with not permitted transition |

| Reserved        | 0x130   | 7 5  | w           | r          |                                                                                                                           |

| Appl. specific  | 0x130   | 15 8 | w           | r          |                                                                                                                           |

## 4.3.3 AL Status Code (address 0x0134:0x0135)

| Parameter | Address | Bit | ZA<br>Drive | ZA<br>ECAT | Description     |

|-----------|---------|-----|-------------|------------|-----------------|

| Status    | 0x134   | 7 0 | w           | r          | See table below |

| Status    | 0x135   | 7 0 | w           | r          | See table below |

| Code   | Description                                             | Current status<br>(change of state)               | Resulting status   |

|--------|---------------------------------------------------------|---------------------------------------------------|--------------------|

| 0x0000 | No error                                                | All                                               | Current status     |

| 0x0011 | Faulty change of state request                          | I -> S, I -> O, P -> O,<br>O -> B, S -> B, P -> B | Current status + E |

| 0x0017 | Incorrect synchron-<br>isation manager<br>configuration | P -> S, S -> O                                    | Current status + E |

| 0x001A | Synchronisation er-<br>ror                              | 0 S -> 0                                          | S + E              |

Other codes are not supported.

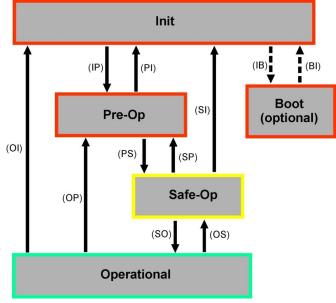

## 4.3.4 EtherCAT communication phases

#### INIT:

Initialisation, no communication

#### PRE-OP:

Mailbox active, parametrising Slave and Startup parameters

#### SAVE-OP:

Cyclical actual values are transmitted, and the servo amplifier tries to synchronise itself.

### **OPERATIONAL**:

Cyclical set values are processed, torque release can be started and the servo amplifier must be synchronised.

Description of the individual communication transitions

| Trans-<br>ition | AL Control<br>(Bit 3 0) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-----------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| (IB)            | 0x03                    | Hardware reset requirement by the control.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| (BI)            |                         | Hardware reset on the servo amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| (IP)            | 0x02                    | Activation of the mailbox (SyncManager 0 and 1) and activation<br>of the amplifier synchronisation routine. As the EC interface does<br>not yet created cyclical interrupts, the warning n17 (no sync.) ap-<br>pears in the amplifier.                                                                                                                                                                                                                                           |  |

| (PI)            | 0x01                    | Deactivation of all EtherCAT Events except AL control and stop-<br>ping of mailbox activities.                                                                                                                                                                                                                                                                                                                                                                                   |  |

| (PS)            | 0x04                    | The amplifier checks the communication configuration specified<br>by the Master in status Pre-Op. Non-fatal errors are deleted auto-<br>matically (no COLDSTART).                                                                                                                                                                                                                                                                                                                |  |

|                 |                         | Mapping of various set and actual values (PDO mapping). The<br>mapping can be preset by the mailbox. The ECAT interface pro-<br>ducers cyclical interrupts and therefore cyclical actual values are<br>available to the EAT interface. The amplifier starts synchronising<br>with the cyclical IRQ of the ECAT interface. The Pro_In and<br>Pro_Out events are activated, which are responsible for the cyc-<br>lical set (Pro_Out) and actual values (Pro_In) of the amplifier. |  |

| (SP)            | 0x02                    | The ECAT interface no longer produces cyclical interrupts.<br>Therefore the warning for lost synchronisation in the amplifier<br>(in17) and the actual values are not activated further.                                                                                                                                                                                                                                                                                         |  |

| Trans-<br>ition | AL Control<br>(Bit 3 0) | Description                                                                                                                                                                                                                                                                                                                                                   |  |

|-----------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| (SI)            | 0x01                    | Deactivate all EtherCAT Events except AL Control. In addition,<br>the ECAT interface does not send any more interrupts, and the<br>amplifier loses synchronisation (warning n17) and it no longer up-<br>dates the actual values. Also, all mailbox activities are stopped.                                                                                   |  |

| (SO)            | 0x08                    | The amplifier finishes this transition only when synchronisation has been performed, the synchronisation warning (n17) is de-<br>leted. Otherwise a synchronisation error (F28) is set after a time-<br>out period. This transition enables the editing of the control word<br>and therefore the acceptance and processing of the cyclical PDC<br>set values. |  |

| (OS)            | 0x04                    | Locking the set value acceptance                                                                                                                                                                                                                                                                                                                              |  |

| (OP)            | 0x02                    | The ECAT interface no longer produces cyclical interrupts.<br>Therefore the warning for lost synchronisation in the amplifier<br>(in17) and the actual values are not activated further.                                                                                                                                                                      |  |

| (OI)            | 0x01                    | Deactivate all EtherCAT Events except AL Control. In addition,<br>the ECAT interface does no longer send interrupts, and the amp-<br>lifier loses synchronisation (warning n17) and it no longer up-<br>dates the actual values. Stopping of a mailbox activities.                                                                                            |  |

## 4.4 CANopen over EtherCAT (CoE) state machine

The state machine for control word and status word corresponds to the CANopen state machine according to DA402. Control word and status word can be found in any fixed PDO mapping. The status word is updated and written only in **Safe-Op** and **Opera-tional** states by the amplifier.

The control word is read in only in **Operational** state.

## 4.4.1 Description of states

| State                     | Description                                                                                                                                                                                                                                                                                 |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Not Ready to Switch<br>On | Servo amplifier is not ready to switch on; the amplifier has not signalled operational readiness (BTB). The servo amplifier is still in the boot phase or in an error state.                                                                                                                |

| Switch On Disable         | In the 'Switch On Disable' state the amplifier cannot be enabled<br>by the EtherCAT interface, e.g. because there is no power<br>switched on.                                                                                                                                               |

| Ready to Switch On        | In the 'Ready to Switch On' status the servo amplifier must be brought to the enable state using the control word.                                                                                                                                                                          |

| Switched On               | In 'Switched On' status the amplifier is enable, however the set values of the EtherCAT interface are not yet accepted. The amplifier is in standstill and a positive edge in Bit 3 of the control word switches on the actual value acceptance (transition to the Operation Enable state). |

| Operation Enable          | In this state the servo amplifier is enabled and set values are accepted from the EtherCAT interface.                                                                                                                                                                                       |

| Quick Stop Active         | The servo amplifier follows a quick stop ramp.                                                                                                                                                                                                                                              |

| Fault Reaction Active     | The servo amplifier reacts to a fault with an E-STOP ramp.                                                                                                                                                                                                                                  |

| Fault                     | A fault is present, the drive has been stopped and locked.                                                                                                                                                                                                                                  |

## 4.4.2 Commands in the control word

The servo amplifier evaluated the individual Bits of the control word.

Commands in the control word for a change of state:

| Transition | Bit 7<br>Reset<br>error | Bit 3<br>General<br>set value<br>enable | Bit 2<br>Enable for<br>Bit 3 and<br>display Bit 5 in<br>the<br>status word | Bit 1<br>Cancel<br>switch on<br>disable | Bit 0<br>Switch on<br>(enable)<br>when<br>Bit 1 = 1 |

|------------|-------------------------|-----------------------------------------|----------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------|

| 0          | Х                       | Х                                       | X                                                                          | Х                                       | Х                                                   |

| 1          | Х                       | х                                       | Х                                                                          | 0                                       | Х                                                   |

| 2          | Х                       | X                                       | X                                                                          | 1                                       | 0                                                   |

| 3          | Х                       | X                                       | 1                                                                          | 1                                       | Р                                                   |

| 4          | Х                       | Р                                       | 1                                                                          | 1                                       | 1                                                   |

| 5          | Х                       | N                                       | 1                                                                          | 1                                       | 1                                                   |

| 5          | Х                       | Х                                       | N                                                                          | 1                                       | 1                                                   |

| 6          | Х                       | X                                       | x                                                                          | 1                                       | N                                                   |

| 7          | Х                       | X                                       | x                                                                          | N                                       | Х                                                   |

| 8          | Х                       | X                                       | X                                                                          | 1                                       | N                                                   |

| 9          | Х                       | X                                       | X                                                                          | N                                       | Х                                                   |

| 10         | Х                       | х                                       | X                                                                          | N                                       | Х                                                   |

| 11         | Х                       | 1                                       | N                                                                          | 1                                       | 1                                                   |

| 12         | Х                       | Х                                       | X                                                                          | N                                       | Х                                                   |

| 13         | Х                       | 1                                       | 1                                                                          | 1                                       | 1                                                   |

| 14         | Х                       | 1                                       | 1                                                                          | 1                                       | 1                                                   |

| 15         | Р                       | Х                                       | X                                                                          | Х                                       | Х                                                   |

Legend

X Bits are irrelevant

1/0 Status of the individual bits

P Signalises a positive edge in the Bit

N Signalises a negative edge in the Bit

| Bit | Action                                                                                                                                                                                          |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Enable the servo amplifier when the switch-on disable is cancelled (Bit1 = 1).                                                                                                                  |

| 1   | Cancelling the switch-on disable.                                                                                                                                                               |

| 2   | Activate the display of Bit 5 in the status word when Bit 0 & Bit 1 = 1 enable for Bit 3 in the control word                                                                                    |

| 3   | Set value enable when Bit0, Bit1 and Bit2 = 1.                                                                                                                                                  |

| 7   | Delete error, transmit command (CLRFAULT). With a set Bit 19 of the AS-<br>CII parameter SERCSET and a present fault that involves a hardware re-<br>set, the servo amplifier generated an F29. |

| 15  | Start of a reference run, when the drive is in the operating mode referen-<br>cing (OPMODE 8).                                                                                                  |

| 12  | Transmit a SAVE command.                                                                                                                                                                        |

Action with positive edges in the control word Bits:

Action with negative edges in the control word Bits:

| Bit |                                                                                                                                |

|-----|--------------------------------------------------------------------------------------------------------------------------------|

| 0   | Switch off drive (transmit the ASCII command DS).                                                                              |

| 1   | If Bit 1 has no negative edge, brake and disable with the ramp DECSTOP.                                                        |

| 2   | When Bit 1 and Bit 2 do not show negative edges, brake with the ramp DECDIS and remain enabled.                                |

| 3   | Switch off set value acceptance from the EtherCAT interface and stop the drive in the operating mode speed control (OPMODE 0). |

| 7   | Delete fault (CLRFAULT), delete command channel.                                                                               |

| 15  | Delete reference run command channel.                                                                                          |

| 12  | Delete SAVE command channel.                                                                                                   |

### 4.4.3 Bits of the status machine (status word)

| Status                       | Bit 6 =<br>Switch-on<br>disable<br>active | Bit 5 =<br>No E-<br>STOP<br>active | Bit 3 =<br>Error | Bit 2 =<br>Operation<br>enabled | Bit 1 =<br>Switched<br>on | Bit 0 =<br>Ready to<br>switch on |

|------------------------------|-------------------------------------------|------------------------------------|------------------|---------------------------------|---------------------------|----------------------------------|

| Not Ready<br>to Switch<br>On | 1                                         | x                                  | 0                | 0                               | 0                         | 0                                |

| Switch On<br>Disabled        | 1                                         | Х                                  | 0                | 0                               | 0                         | 0                                |

| Ready to<br>Switch On        | 0                                         | Х                                  | 0                | 0                               | 0                         | 1                                |

| Status                     | Bit 6 =<br>Switch-on<br>disable<br>active | Bit 5 =<br>No E-<br>STOP<br>active | Bit 3 =<br>Error | Bit 2 =<br>Operation<br>enabled | Bit 1 =<br>Switched<br>on | Bit 0 =<br>Ready to<br>switch on |

|----------------------------|-------------------------------------------|------------------------------------|------------------|---------------------------------|---------------------------|----------------------------------|

| Switch On                  | 0                                         | 1                                  | 0                | 0                               | 1                         | 1                                |

| Operation<br>Enable        | 0                                         | 1                                  | 0                | 1                               | 1                         | 1                                |

| Fault                      | 0                                         | 1                                  | 1                | 0                               | 0                         | 0                                |

| Fault reac-<br>tion active | 0                                         | 0                                  | 1                | 1                               | 1                         | 1                                |

| Quick Stop<br>Active       | 0                                         | 0                                  | 0                | 0                               | 1                         | 1                                |

Legend

X Bits are irrelevant

1/0 Status of the individual bits

#### Additional Information

| Bit 4 1 = Intermediate circuit voltage is preser | te circuit voltage is present | Bit 4 1 = Intermediate |

|--------------------------------------------------|-------------------------------|------------------------|

|--------------------------------------------------|-------------------------------|------------------------|

- Bit 7 1 = A warning is present at the device

- Bit 8 1 = Position error present (in all position modes (OPMODE = 4, 5, 6, 8))

- Bit 10 1 = Target reached (in position)

- Bit 11 1 = Restrictions active (e.g. hardware or software end switch has triggered)

- Bit 12 1 = Reference run active

- Bit 13 1 = Reference run error

- Bit 15 1 = Motion task active (in profile position mode)

## 4.5 Implemented operating modes

The following operating modes are implemented via the object 0x6060:

- cyclic synchronous position mode 0x08 and 0xFA

- cyclic synchronous velocity mode 0x09 and 0xFE

- cyclic synchronous torque mode 0x0A and 0xFD

- homing mode 0x06 and 0xF9

The negative values correspond to the manufacturer-specific settings such as the OP-MODE command.

## 4.6 Setting the EtherCAT cycle time

The cycle time used in the servo amplifier for the cyclical set and actual values can be present either configured in the amplifier in the parameter PTBASE or it can be configured in the start phase.

This is performed via a mailbox SDO access (see Mailbox Handling [44 25]) to the CANopen objects 0x60C2 Subindex 1 und 2.

The subindex 2, called interpolation time index, defines the power of ten of the time value (e.g. -3 corresponds to  $10^{-3}$ , that is millisecond) while the subindex 1 called time units", specifies the number of units (e.g. 4 for 4 units).

If you want to run a cycle time of 2 ms this can be specified via various combinations,m e.g. via:

Index = -3, Units = 2 or Index = -4, Units = 20 etc.

The parameter PTBASE is counted in increments of 250 microseconds inside the device. 2 ms correspond to a PTBASE of 8, for example.

## 4.7 Recommended cycle time based on the operating modes

With the servo amplifier, the minimum cycle time depends very much of the drive configuration (second actual position value encoder, latching). The analogue evaluation of the drives should be deactivated, if possible (ANOUT1=0, ANOUT2=0, ANCNFG= -1).

| Interface | Cycle time PMCprotego D |

|-----------|-------------------------|

| Position  | ³ 0.25 ms (³ 250 μs)    |

| Speed     | ³ 0.25 ms (³ 250 μs)    |

| Torque    | ³ 0.25 ms (³ 250 μs)    |

## 4.8 Synchronisation based on the cycle time

With all the Pilz servo amplifiers the internal PLLL can compensate a mean deviation from the cycle time specified by the Mater of up to 1000 ppm. This means, for example that with a set cycle time of 1 ms the drive can still synchronise itself with a mean deviation in the cycle time specified by the master of up to +/- 1µs with its internal PLL. The mean deviation of the cycle time is understood to be the mean length of all cycles.

The servo amplifier enables to report the following jitter in the master cycle time without a synchronisation error, depending on the set cycle time:

Cycle time >= 1ms  $\rightarrow$  permitted jitter = 320  $\mu s$

Cycle time <= 750  $\mu s \rightarrow$  permitted jitter = 70  $\mu s$

In the second consecutive mater interrupts, outside the permitted jitter, the drive signals a synchronisation error F28 and/or warning F17. The synchronisation monitoring can be switched off with the ASCII command SERCSET Bit 17 and 18.

## 4.9 Latch- control word and latch status word

Latch control word (2 Byte):

| Bit     | Value (bin)       | Value (hex) | Description                             |

|---------|-------------------|-------------|-----------------------------------------|

| 0       | 0000000 0000001   | xx01        | Enable external latch 1 (positive rise) |

| 1       | 0000000 00000010  | xx02        | Enable external latch 1 (negative rise) |

| 2       | 0000000 00000100  | xx04        | Enable external latch 2 (positive rise) |

| 3       | 0000000 00001000  | xx08        | Enable external latch 2 (negative rise) |

| 4       | 0000000 00010000  | Xx10        | Enable internal latch C (positive rise) |

| 5 - 7   |                   |             | Reserved                                |

| 8 – 12  | 0000001 0000000   | 01xx        | Read external latch 1 (positive rise)   |

|         | 00000010 00000000 | 02xx        | Read external latch 1 (negative rise)   |

|         | 00000011 00000000 | 03xx        | Read external latch 2 (positive rise)   |

|         | 00000100 00000000 | 04xx        | Read external latch 2 (negative rise)   |

|         | 00000101 00000000 | 05xx        | Read external latch C (positive rise)   |

| 13 - 15 |                   |             | Reserved                                |

Latch status word (2 Byte):

| Bit    | Value (bin)       | Value (hex) | Description                                        |

|--------|-------------------|-------------|----------------------------------------------------|

| 0      | 0000000 00000001  | xx01        | External latch 1 valid (positive rise)             |

| 1      | 0000000 00000010  | xx02        | External latch 1 valid (negative rise)             |

| 2      | 0000000 00000100  | xx04        | External latch 2 valid (positive rise)             |

| 3      | 0000000 00001000  | xx08        | External latch 2 valid (negative rise)             |

| 4      | 0000000 00010000  | Xx10        | Internal latch C valid (positive rise)             |

| 5 - 7  |                   |             | Reserved                                           |

| 8 – 11 | 00000001 00000000 | 01xx        | Acknowledge value external latch 1 (positive rise) |

|        | 00000010 00000000 | 02xx        | Acknowledge value external latch 1 (negative rise) |

| Bit     | Value (bin)       | Value (hex) | Description                                        |

|---------|-------------------|-------------|----------------------------------------------------|

|         | 00000011 00000000 | 03xx        | Acknowledge value external latch 2 (positive rise) |

|         | 00000100 00000000 | 04xx        | Acknowledge value external latch 2 (negative rise) |

|         | 00000101 00000000 | 05xx        | Acknowledge value internal latch C (positive rise) |

| 12 - 15 | 00010000 00000000 | 1xxx        | State Digital Input 4                              |

|         | 00100000 00000000 | 2xxx        | State Digital Input 3                              |

|         | 0100000 0000000   | 4xxx        | State Digital Input 2                              |

|         | 1000000 0000000   | 8xxx        | State Digital Input 1                              |

## 4.10 Mailbox Handling

With EtherCAT the acyclical data traffic (object channel or SDO channel) is called mailbox. The approach of the Master is considered:

| Mailbox Output | Data are sent from the Master (EtherCAT control) to the Slave (servo amplifier). It is a requirement (read/write) of the master. The Mailbox Output runs via the Sync Manager 0. |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mailbox Input  | Data are sent from the Slave (Servo amplifier) to the Master (EtherCAT control). The Master reads the answer from the slave. The Mailbox Input runs via Sync Manager 1.          |

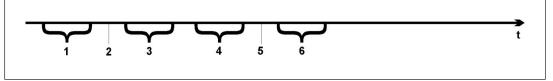

The Timing diagram illustrated the processing of a mailbox access:

#### Legend

- 1 EtherCAT Master writes the mailbox request in the Mail Out Buffer.

- 2 At the next interrupt, the EtherCAT interface triggers a Sync Manager 0 Event (Mailbox Output Event) in the AL Event Register.

- 3 The servo amplifier reads 16 Byte from the Mail Out Buffer and copies it into an internal Mailbox Output Array.

- 4 The servo amplifier detects new files in the internal mailbox output array, and it executes the SDO access to the object requested by the EtherCAT interface. The reply from the servo amplifier is written to an internal Mailbox Input Array.

- 5 The servo amplifier deleted all the data in the internal Mailbox Output Array and paves the way for a new mailbox access.

- 6 The servo amplifier copies the response telegram from the internal Mailbox Input Array into the mail in the buffer of the EtherCAT interface.

## 4.10.1 Mailbox Output

An interrupt of the EtherCAT interface with a Sync Manager 0 - Event starts a Mailbox Output process. A 1 in the Mail Out Event-Bit of the AL Event Registers signalised to the servo amplifier that the EtherCAT interface wants to transmit a mailbox news and that it has already stored the requested data in the Mail Out Buffer. The servo amplifier reads in the IRQ routine 16 byte from the Mail Out Buffer.

| Meaning | of the | individual | bytes:         |

|---------|--------|------------|----------------|

| mouning | 01 110 | manuada    | <i>by</i> 100. |

| Addre             | ess ( | 0x1800                                                                                       |                                                     |        |         |         |         | Address 0x180F    |       |        |       |      |         |       |     |

|-------------------|-------|----------------------------------------------------------------------------------------------|-----------------------------------------------------|--------|---------|---------|---------|-------------------|-------|--------|-------|------|---------|-------|-----|

| 0                 | 1     | 2 3 4 5 6 7                                                                                  |                                                     |        |         |         | 7       | 8                 | 9     | 10     | 11    | 12   | 13      | 14    | 15  |

|                   | CAN   | l over l                                                                                     | Ether                                               | CAT s  | oecific | data    | 1       | CAN specific data |       |        |       |      |         |       |     |

|                   |       |                                                                                              | CoE H                                               | leade  | r       |         |         |                   |       | (star  | ndard | CAN  | SDO)    |       |     |

| Byte (            | 0 L   | ength                                                                                        | of the                                              | follow | ving da | ata fro | om By   | te 2 (L           | ow B  | yte)   |       |      |         |       |     |

| Byte <sup>-</sup> | 1 L   | ength                                                                                        | ength of the following data from Byte 2 (High Byte) |        |         |         |         |                   |       |        |       |      |         |       |     |

| Byte 2            | 2     | ddress (Low Byte)                                                                            |                                                     |        |         |         |         |                   |       |        |       |      |         |       |     |

| Byte 3            | 3 A   | Address                                                                                      | s (Higl                                             | h Byte | e)      |         |         |                   |       |        |       |      |         |       |     |

| Byte 4            |       | Bits 0<br>Bit 6                                                                              |                                                     |        | el      |         |         |                   |       |        |       |      |         |       |     |

| Byte &            | 5 E   | Bits 0                                                                                       | . 3: T                                              | уре    |         |         |         |                   |       |        |       |      |         |       |     |

|                   |       | _                                                                                            | 1 = R                                               | eserve | ed: AD  | DS ove  | er Eth  | erCA              | Г     |        |       |      |         |       |     |

|                   |       | _                                                                                            | 2 = R                                               | eserve | ed: Et  | herne   | t over  | Ether             | CAT   |        |       |      |         |       |     |

|                   |       | _                                                                                            | 3 = C.                                              | AN ov  | er Eth  | nerCA   | T)      |                   |       |        |       |      |         |       |     |

|                   | E     | Bits 4                                                                                       | . 7: R                                              | eserv  | ed      |         |         |                   |       |        |       |      |         |       |     |

| Byte 6            | (     | PDO nu<br>Only in<br>or MSE                                                                  | case                                                | of PD  | 0 tra   | nsmis   | sion, I | Bit 0 =           | LSB   | of the | PDO   | numt | ber, se | e Byt | e 7 |

| Byte 7            | E     | Bit 0: MSB of the PDO number, see Byte 6)<br>Bit 1 3: Reserved<br>Bit 4 7: CoE specific type |                                                     |        |         |         |         |                   |       |        |       |      |         |       |     |

|                   |       | -                                                                                            | 0: Re                                               | served | k       |         |         |                   |       |        |       |      |         |       |     |

|                   |       | -                                                                                            | 1: Em                                               | ergen  | cy me   | essage  | е       |                   |       |        |       |      |         |       |     |

|                   |       | -                                                                                            | 2: SD                                               | O req  | uirem   | ent     |         |                   |       |        |       |      |         |       |     |

|                   |       | <ul> <li>3: SDO response</li> </ul>                                                          |                                                     |        |         |         |         |                   |       |        |       |      |         |       |     |

|                   |       | – 4: TXPDO                                                                                   |                                                     |        |         |         |         |                   |       |        |       |      |         |       |     |

|                   |       | -                                                                                            | 5: Rxl                                              | PDO    |         |         |         |                   |       |        |       |      |         |       |     |

|                   |       | -                                                                                            | 6: Re                                               | mote f | ransn   | nissio  | n requ  | lest of           | a Txl | PDO    |       |      |         |       |     |

|                   |       | -                                                                                            | 7: Re                                               | mote f | ransn   | nissio  | n requ  | lest of           | a Rx  | PDO    |       |      |         |       |     |

|                   |       | _                                                                                            | 8 1                                                 | 5: Re  | serve   | d for l | ater a  | pplica            | tions |        |       |      |         |       |     |

| Byte 8     | Control byte in CAN telegram:                                                           |

|------------|-----------------------------------------------------------------------------------------|

|            | <ul> <li>Write access: 0x23=4Byte, 0x27=3Byte, 0x2B=2Byte, 0x2F=1Byte</li> </ul>        |

|            | <ul> <li>Read access: 0x40</li> </ul>                                                   |

| Byte 9     | Low Byte of the CAN object number (index)                                               |

| Byte<br>10 | High Byte of the CAN object number (index)                                              |

| Byte<br>11 | Subindex in accordance with the CANopen specification for the Pilz servo ampli-<br>fier |

| Byte<br>12 | Data in case of a write access (Low Byte)                                               |

| Byte<br>13 | Data in case of a write access                                                          |

| Byte<br>14 | Data in case of a write access                                                          |

| Byte<br>15 | Data in case of a write access (High Byte)                                              |

The servo amplifier responds to each telegram with a response in the Mailbox Input Buffer.

## 4.10.2 Mail Input

Te serve amplifier responds to each CoE telegram with a 16 Byte response telegram in the Mailbox Input Buffer. The Bits are defined as follows:

| Addr | Address 0x1C00 |                                                                                                        |        |        |         |        |        |      | Address 0x1C0F |       |       |          |      |    |    |

|------|----------------|--------------------------------------------------------------------------------------------------------|--------|--------|---------|--------|--------|------|----------------|-------|-------|----------|------|----|----|

| 0    | 1              | 2                                                                                                      | 3      | 4      | 5       | 6      | 7      | 8    | 9              | 10    | 11    | 12       | 13   | 14 | 15 |